| |

|

中科院微电子所在动态随机存储器研究领域获进展(附图)(2022-7-1)

DRAM是存储器领域最重要的分支之一。随着尺寸微缩,传统1T1C结构的DRAM存储电容限制问题以及相邻存储单元之间的耦合问题愈发显著,导致DRAM进一步微缩面临挑战。基于铟镓锌氧(IGZO)晶体管的2T0C-DRAM有望克服1T1C-DRAM的微缩挑战,在3D

DRAM方面发挥更大优势。但目前研究工作都基于平面结构的IGZO器件,形成的2T0C单元尺寸(大约20F2)比相同特征尺寸下的1T1C单元尺寸(6F2)大很多,使得IGZO-DRAM缺少密度优势。 针对平面结构IGZO-DRAM的密度问题,中国科学院院士、中科院微电子研究所研究员刘明团队与华为海思团队联合在2021年IEDM国际大会报道的垂直环形沟道结构IGZO

FET的基础上,再次成功将器件的关键尺寸(CD)微缩至50

nm。微缩后的IGZO

FET具有优秀的晶体管特性,包括约32.8

μA/μm的开态电流(Vth

+ 1 V时)和约92

mV/dec的亚阈值摆幅。同时,器件在-40

℃到120

℃的温度范围内表现出了良好的热稳定性和可靠性。

该研究成果有助于推动IGZO晶体管在高密度3D

DRAM领域的应用。基于该成果的文章Vertical Channel-All-Around (CAA) IGZO FET under 50 nm CD with High Read

Current of 32.8 μA/μm

(Vth + 1 V), Well-performed Thermal Stability up to 120 ℃ for Low Latency, High-density 2T0C 3D DRAM Application入选2022

VLSI,且获选Highlight文章。

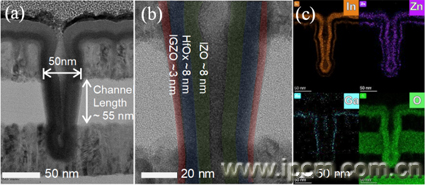

图1

关键尺寸(CD)50 nm的IGZO-CAA

FET的截面电镜图

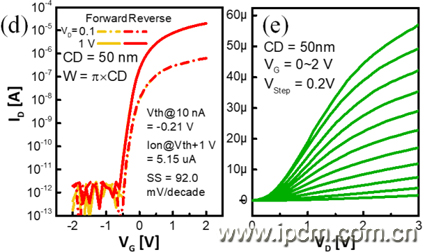

图2

关键尺寸(CD)50 nm的IGZO-CAA

FET的转移输出曲线

|

|

工业控制计算机网站 |

|